| 2 |

|---|

| 3 |

| 4 |

| 5 |

CFP MSA Management Interface

Specification

100/40 Gigabit Transceiver Package Multi-Source Agreement

Version 2.6 r06a

March 24, 2017

jiashu.chen@finisar.com

1

# **CFP MSA Group Contacts**

Jiashu Chen

| _ |  |

|---|--|

| 2 |  |

| J |  |

Technical Editor

| Finisar Corp.                      | Chris Cole    | chris.cole@finisar.com         |

|------------------------------------|---------------|--------------------------------|

| Avago Technologies, Ltd.           | John Petrilla | john.petrilla@avagotech.com    |

| Oclaro Inc.                        | Kiyohisa      | kiyohisa.hiramoto@oclaro.com   |

|                                    | Hiramoto      |                                |

| Sumitomo Electric Industries, Ltd. | Eddie Tsumura | tsumura-eiji@sei.co.jp         |

| Fujitsu Optical Components         | Yasuno        | nagakubo.yasuno@jp.fujitsu.com |

|                                    | Nagakubo      |                                |

| Lumentum                           | David Lewis   | David.lewis@lumentum.com       |

4 5

Copyright © 2008-2017 CFP MSA

| 1              | TABLE OF CONTENTS                                                |    |

|----------------|------------------------------------------------------------------|----|

| 2              | REVISION HISTORY                                                 | 7  |

| 3              | REFERENCES                                                       | 9  |

| 4              | LIST OF FIGURES                                                  | 10 |

| 5              | LIST OF TABLES                                                   | 11 |

| 6              |                                                                  |    |

|                |                                                                  |    |

| 7<br>8         | 1.1 BACKGROUND                                                   |    |

| 9              | 1.3 CFP Management Interface Specification Version Compatibility |    |

| 10             | 1.4 CONTENT OF THIS DOCUMENT                                     |    |

| 11             | 1.5 Notations                                                    |    |

| 12             | 1.5.1 Hardware Signal Name                                       |    |

| 13             | 1.5.2 Soft (MDIO) Signal Name                                    |    |

| 14<br>15       | 1.5.3 CFP Register Name and Address                              |    |

| 16             | 1.5.5 Special Characters                                         |    |

| 17             | 1.6 GLOSSARY                                                     |    |

| 18             | 2 CFP MANAGEMENT INTERFACE                                       |    |

| 19             | 2.1 Overview                                                     |    |

| 20             | 2.1.1 OVERVIEW                                                   |    |

| 21             | 2.1.1.1 CFP/CFP2/CFP4 Common Functionality                       |    |

| 22<br>23       | 2.1.1.2 CFP2 Only Multi-device Type Functionality                | 18 |

| 23             | 2.1.1.3 Configuration of Port Address Support                    |    |

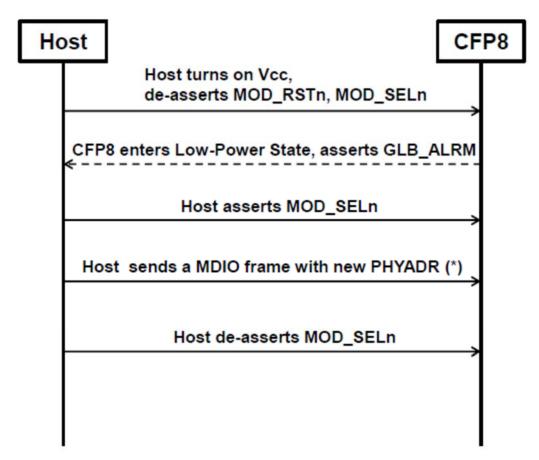

| 24<br>25<br>26 | 2.1.2 CFP8 MDIO Port Address and MOD_SELn                        |    |

| 26             | 2.1.2.1 Shared Bus Address Scheme (Optional)                     | 18 |

| 27             | 2.2 SPECIFICATIONS                                               |    |

| 28             | 2.2.1 Optional Features                                          |    |

| 29<br>30       | 2.2.1.1 Optional Controls                                        |    |

| 31             | 2.2.1.2 Optional FAWS signals                                    |    |

| 32             | 2.4 MDIO MANAGEMENT FRAME STRUCTURE                              |    |

| 33             | 3 CFP REGISTER OVERVIEW                                          | 22 |

| 34             | 3.1 CFP REGISTER SPACE                                           |    |

| 35             | 3.2 Non-volatile Registers (NVRs)                                |    |

| 36             | 3.2.1 CFP NVR Tables                                             |    |

| 37             | 3.2.2 Vendor NVR Tables                                          |    |

| 38             | 3.2.3 User NVR Tables                                            |    |

| 39             | 3.2.4 NVR Content Management                                     |    |

| 40             | 3.2.5 User Private Use Registers                                 |    |

| 41<br>42       | 3.3 VOLATILE REGISTERS (VRS)                                     |    |

| 43             | 3.3.1 CFP Module VR 1 Table                                      |    |

| 44             | 3.3.3 Host Lane Specific Register Table                          |    |

| 45             | 3.4 Module Vendor Private Registers                              |    |

| 46             | 3.5 RESERVED CFP REGISTERS                                       |    |

| 47             | 3.5.1 Un-implemented Registers                                   | 25 |

| 1             | 3.6 CFP Register Data Types                                              | 25 |

|---------------|--------------------------------------------------------------------------|----|

| 2             | 3.6.1 Byte                                                               | 25 |

| 3             | 3.6.2 Word                                                               | 25 |

| 4             | 3.6.3 Bit Field                                                          |    |

| 5             | 3.6.4 Two's Complement                                                   |    |

| 6             | 4 CFP CONTROL AND SIGNALING THEORY                                       | 27 |

| 7             | 4.1 CFP Module States and Related Signals                                |    |

| 8             | 4.1.1 Signals Affecting Transition of CFP Module States                  |    |

| ğ             | 4.1.1.1 Combined Module Reset Signal MOD_RSTs                            |    |

| ١Ŏ            | 4.1.1.2 Combined Module Low Power Signal MOD LOPWRs                      |    |

| 10<br>11      | 4.1.1.3 Combined Transmitter Disable Signal TX DISs                      |    |

| 12<br>13      | 4.1.1.4 Fault Conditions                                                 |    |

| 13            | 4.1.1.5 Minimum Signal Duration                                          | 29 |

| 14            | 4.1.2 Signals Affected by Module Insertion or State Transition           | 29 |

| 4<br> 5<br> 6 | 4.1.2.1 MOD_ABS                                                          | 29 |

| 16            | 4.1.2.2 GLB_ALRM                                                         |    |

| 7             | 4.1.2.3 INIT_DONE                                                        |    |

| 8<br> 9       | 4.1.2.4 HIPWR_ON                                                         |    |

| 19            | 4.1.2.5 MOD_READY (Ready State)                                          |    |

| 20            | 4.1.2.6 MOD_FAULT (Fault State)                                          |    |

| 21            | 4.1.3 CFP Module States                                                  |    |

| 22            | 4.1.3.1 Reset State (Steady)                                             |    |

| 24            | 4.1.3.2 Initialize State (Transient)                                     |    |

| 25            | 4.1.3.4 High-Power-up State (Transient)                                  |    |

| 25<br>26      | 4.1.3.5 TX-Off State (Steady)                                            |    |

| <u> </u>      | 4.1.3.6 TX-Turn-on State (Transient)                                     |    |

| 28            | 4.1.3.7 Ready State (Steady)                                             |    |

| 29            | 4.1.3.8 TX-Turn-off State (Transient)                                    |    |

| 30            | 4.1.3.9 High-Power-Down State (Transient)                                |    |

| 31            | 4.1.3.10 Fault State (Steady)                                            | 33 |

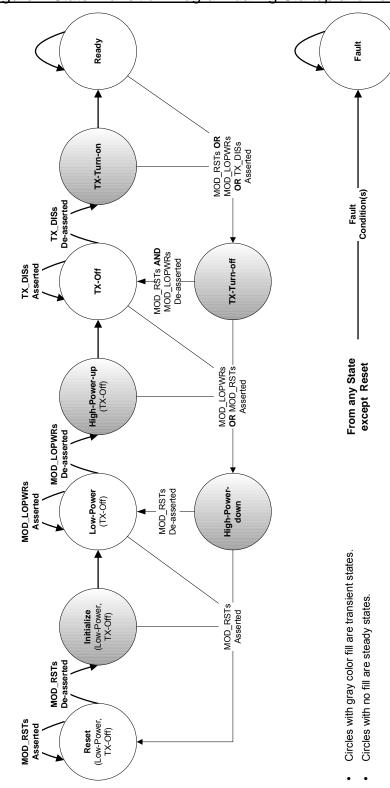

| 32            | 4.2 STATE TRANSITION DIAGRAM                                             |    |

| 33            | 4.3 EXAMPLES OF MODULE STARTUP AND TURN-OFF SEQUENCE                     |    |

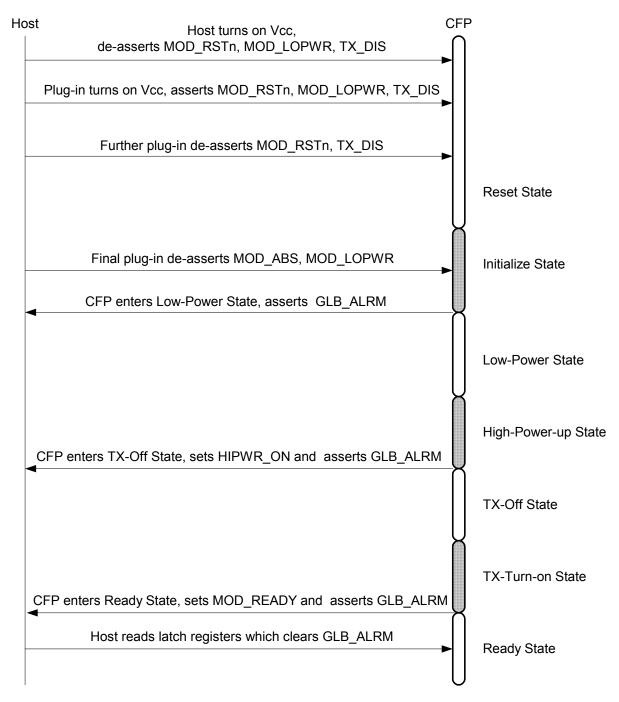

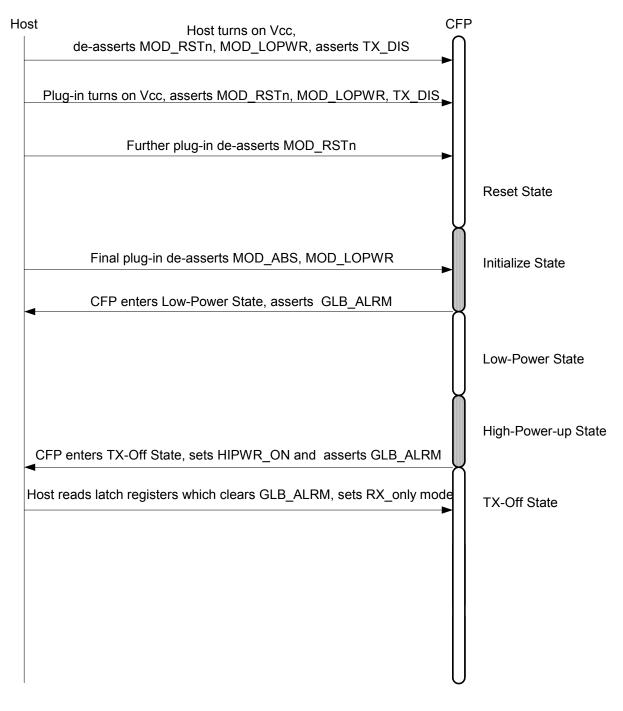

| 34            | 4.3.1 Power-up CFP Module to Ready State without Host Transition Control | 35 |

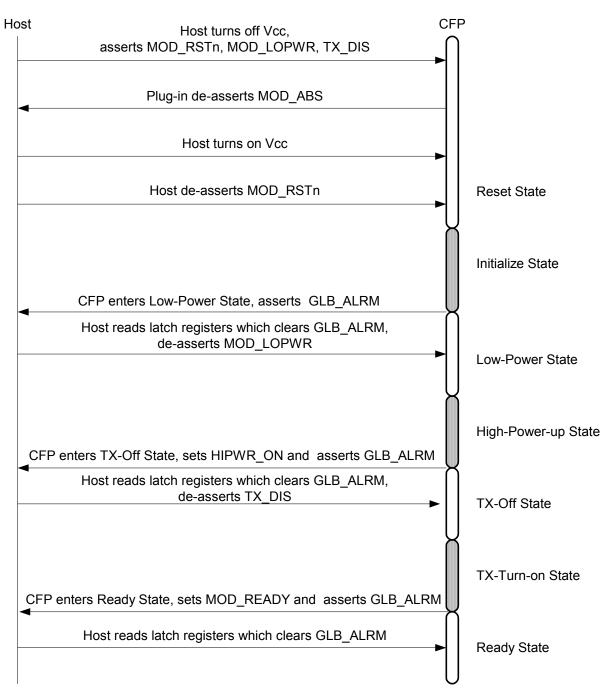

| 35            | 4.3.2 Power-up the Module with Full Host Transition Control              | 36 |

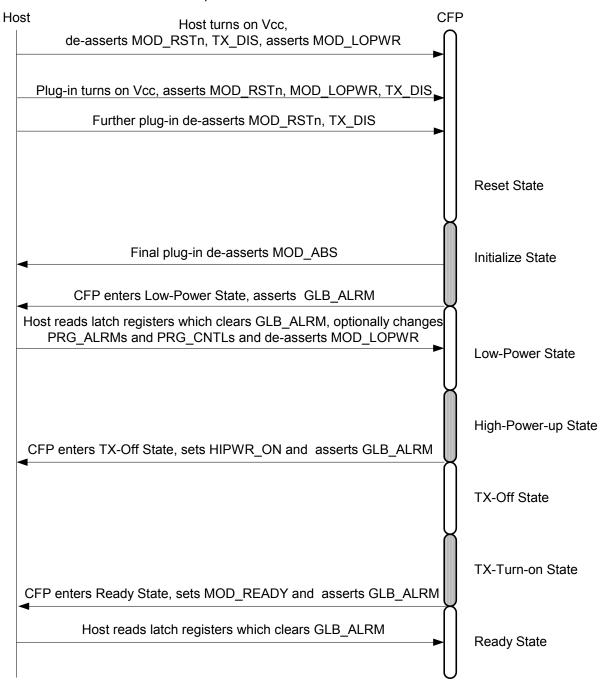

| 36            | 4.3.3 Power-Up the Module with Some Host Transition Control              | 36 |

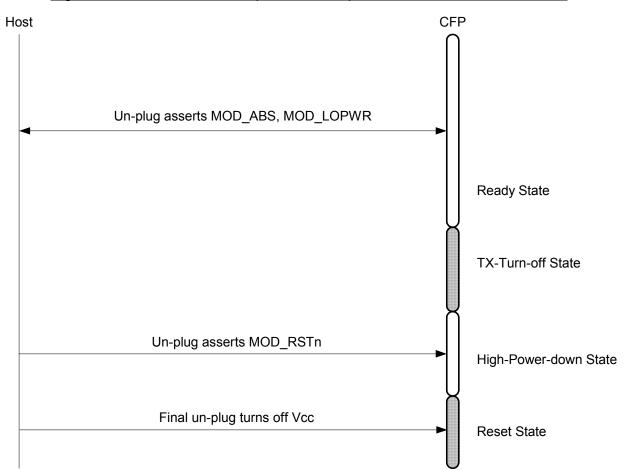

| 37            | 4.3.4 Example of Module Turn-off Sequence                                | 36 |

| 38            | 4.4 Special Modes of Operation                                           | 36 |

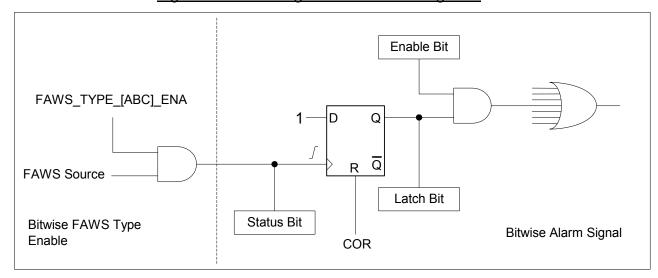

| 39            | 4.5 BEHAVIOR OF FAWS IN CFP STATES                                       | 42 |

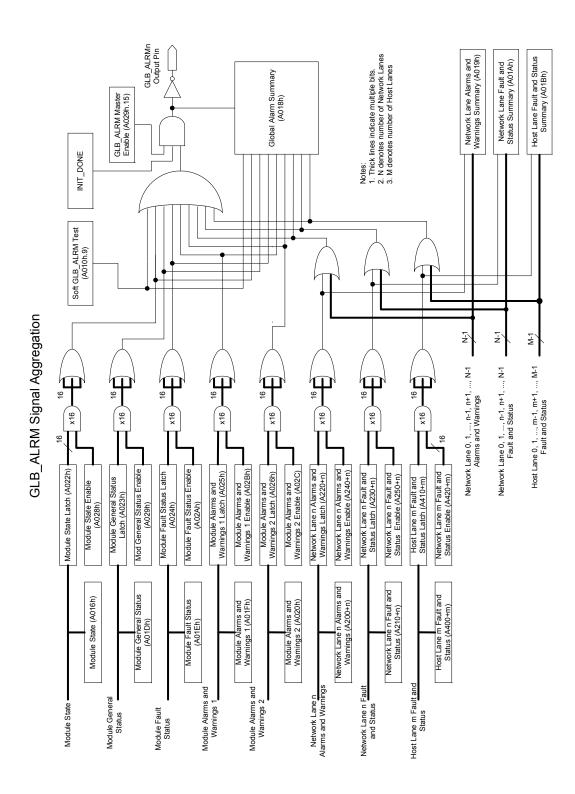

| 10            | 4.6 GLOBAL ALARM SYSTEM LOGIC                                            |    |

| 11            | 4.6.1 Latched and Summary Registers Synchronization                      |    |

| 12            | 4.7 SPECIFIC HOST CONTROLS OVER MANAGEMENT INTERFACE                     |    |

| 13            | 4.7.1 Soft Module Reset (A010h.15) Function                              |    |

| 14            | 4.7.2 Soft Global Alarm Test (A010h.9) Function                          |    |

| 15            | 4.8 TIMING FOR MANAGEMENT INTERFACE CONTROL AND STATUS REPORTING         |    |

| 16            | 4.8.1 Miscellaneous Timing                                               |    |

| 17            | 4.9 BIT ERROR RATE CALCULATION                                           |    |

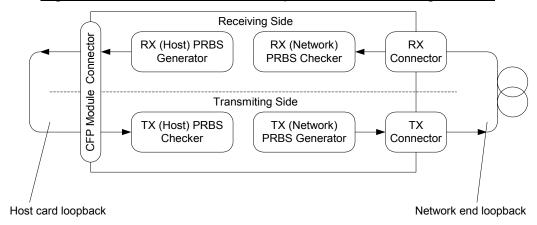

| 18            | 4.9.1 Network Lane PRBS Setup                                            |    |

| 19            | 4.9.2 Network Lane BER Calculation                                       |    |

| 50            | 4.9.3 Host Lane PRBS Control                                             |    |

| 51            | 4.9.4 Host Lane BER Calculation                                          |    |

| 52            | 4.10 CFP REGISTER ACCESS                                                 |    |

| 53            | 4.10 CFP REGISTER ACCESS                                                 |    |

| 54            | 4.10.1.1 4.10.1.1 Password Control (Optional)                            |    |

| , T           | T. 10. 1. 1 T. 10. 1. 1 1 000WUIU OUIIIIUI (ODIIIUIIII)                  |    |

| 1                          | 4.10.2 User NVR Restore and Save Functions                                       |     |

|----------------------------|----------------------------------------------------------------------------------|-----|

| 2                          | 4.10.2.1 User NVR Restore and Save Command (Bit 5)                               | 52  |

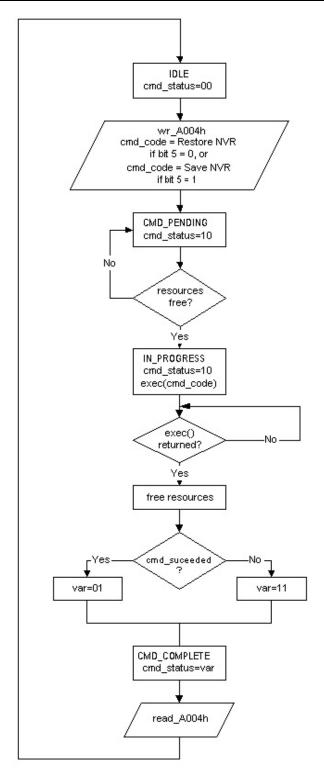

| 234567                     | 4.10.2.2 Restore and Save Command State Definitions                              |     |

| 4                          | 4.10.2.3 State Machine Function Definitions                                      |     |

| 5                          | 4.10.2.4 Command Status (bits 3, 2)                                              | 53  |

| 6                          | 4.10.2.5 Extended Commands (bits 1, 0)                                           | 54  |

|                            | 4.10.2.6 NVR Data Safety in Save Function                                        |     |

| 8                          | 4.11 SETUP OF PROGRAMMABLE CONTROL AND ALARM PINS                                |     |

| 9                          | 4.11.1 Relationship between HW PIN PRG_CNTLx, MDIO PRG_CNTLx Pin State, and MDIC |     |

| 1Ŏ                         |                                                                                  |     |

| _                          | PRG_CNTLx                                                                        |     |

| 11                         | 4.11.2 Programmable Control Functions for PRG_CNTLs                              |     |

| 12                         | 4.11.3 Programmable Alarm Sources for PRG_ALRMs                                  | 56  |

| 13                         | 4.12 COMMON DATA BLOCK                                                           | 57  |

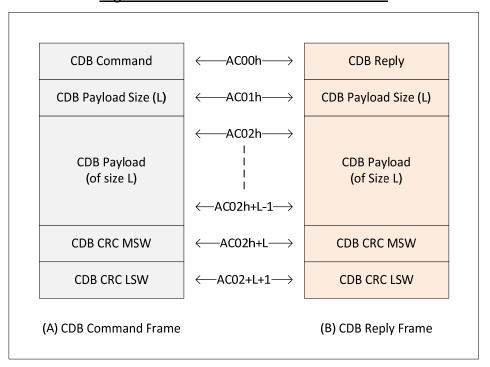

| 14                         | 4.12.1 CDB Structure                                                             | 57  |

| 15                         | 4.12.1.1 CDB Command Frame                                                       |     |

| 1ĕ                         | 4.12.1.2 CDB Reply Frame                                                         |     |

| iŏ                         | 4.12.2 CDB Implementation                                                        |     |

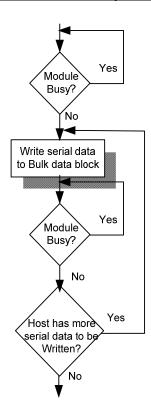

| 18                         | 4.12.2.1 Write Flow Control on CDB                                               | oc  |

| 19                         |                                                                                  |     |

|                            |                                                                                  |     |

| 20                         | 4.12.2.3 Password Control                                                        |     |

| 2 I                        | 4.12.2.4 Interaction with Register A004h                                         | 61  |

| 22                         | 4.12.2.5 Interrupt to Host                                                       | 61  |

| 20<br>21<br>22<br>23<br>24 | 4.12.2.6 CRC Option                                                              |     |

| <u> </u>                   | 4.12.2.7 Initialization                                                          |     |

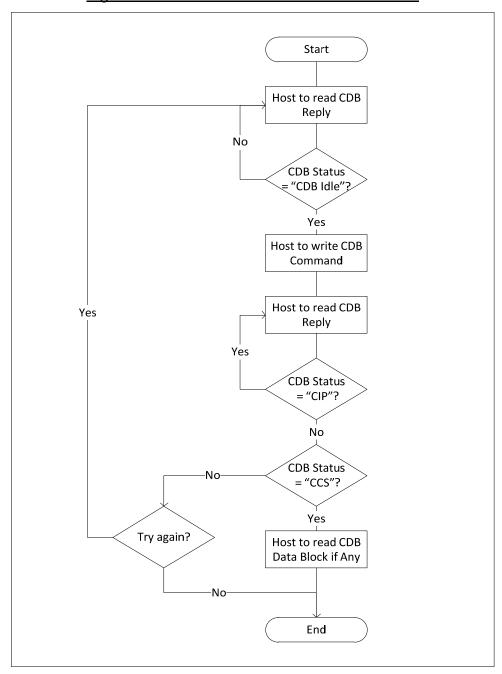

| 25                         | 4.12.3 CDB Command Execution                                                     |     |

| 26<br>27                   | 4.12.3.1 Host to Write a CDB Command Frame                                       | 61  |

| 27                         | 4.12.3.2 Host to Read a CDB Reply Frame                                          | 61  |

| 28                         | 4.12.3.3 CDB Command Execution Process                                           | 62  |

| 29                         | 4.12.4 CDB Commands and Applications                                             | 62  |

| 30                         | 4.12.4.1 Single Command Task                                                     |     |

| 31                         | 4.12.4.2 Multiple Command Task                                                   | 62  |

| 32                         | 4.12.5 CDB Command Table                                                         |     |

| 33                         | 4.13 MULTI-LINK GEARBOX (MLG) SUPPORT (OPTIONAL)                                 |     |

|                            |                                                                                  |     |

| 34                         | 5 CFP REGISTER DESCRIPTION                                                       | 68  |

| 35                         | 5.1 CFP NVR 1 TABLE: BASE ID REGISTERS                                           | 68  |

| 36                         | 5.2 CFP NVR 2 TABLE: ALARM/WARNING THRESHOLD REGISTERS                           | 77  |

| 37                         | 5.3 CFP NVR 3 TABLE: NETWORK LANE BOL MEASUREMENT REGISTERS                      |     |

| 38                         | 5.4 CFP NVR 4 TABLE: METWORK LANE BOE MEAGOREMENT REGIOTERS                      |     |

| 39                         |                                                                                  |     |

|                            | 5.5 CFP Module VR 1 Table                                                        |     |

| 40                         | 5.5.1 CFP Command/Setup Registers                                                |     |

| 41                         | 5.5.1.1 NVR Access Control (A004h)                                               |     |

| 42                         | 5.5.1.2 PRG_CNTLs Function Select (A005h, A006, A007h)                           |     |

| 43                         | 5.5.1.3 PRG_ALRMs Source Select (A008h, A009h, A00Ah)                            |     |

| 44                         | 5.5.1.4 Module Bi-/Uni- Directional Operating Mode Select (A00Bh)                | 85  |

| 45                         | 5.5.2 Module Control Registers (A010h~A015h)                                     | 85  |

| 46                         | 5.5.3 Module State Register (A016h)                                              |     |

| 47                         | 5.5.4 Module Alarm Summary Registers (A018h, A019h, A01Ah, A01Bh)                |     |

| 48                         | 5.5.5 Module FAWS Registers (A01Dh, A01Eh, A01Fh, A020h)                         |     |

|                            | 5.5.5 Madiula FAMO Latab Daniatara (A0001: A0001: A0001: A0001: A0001:           | 00  |

| 49                         | 5.5.6 Module FAWS Latch Registers (A022h, A023h, A024h, A025h, A026h)            |     |

| 50                         | 5.5.7 Module FAWS Enable Registers (A028h, A029h, A02Ah, A02Bh, A02Ch)           |     |

| 51                         | 5.5.8 Module Analog A/D Value Registers (A02Fh, A030h, A031h, A032h, A033h)      | 86  |

| 52                         | 5.5.9 Module PRBS Registers (A038h, A039h)                                       |     |

| 53                         | 5.6 MLG MANAGEMENT INTERFACE REGISTER TABLE                                      |     |

| 54                         | 5.7 NETWORK LANE SPECIFIC REGISTER TABLES                                        |     |

| 55                         | 5.8 HOST LANE SPECIFIC REGISTER TABLE                                            |     |

|                            | U.U TIOUT LANE OF LOTE TO INCOMPLET TABLE                                        | 103 |

\_\_\_\_\_

| 1                | 6 MSA-100GLH AND OTHER COHERENT MODULE MANAGEMENT INTERF               | ACE 112 |

|------------------|------------------------------------------------------------------------|---------|

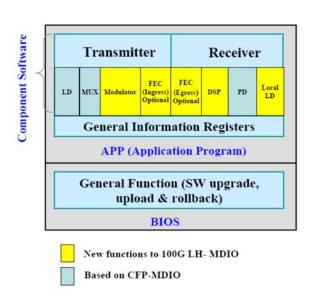

| 2                | 6.1 Overview                                                           | 112     |

| 3                | 6.2 MSA-100GLH MODULE MANAGEMENT INTERFACE INFORMATION & FUNCTIONALITY | 113     |

| 4                | 6.2.1 Module Base and Extended ID Information                          |         |

| 5                | 6.2.2 Module Command, Control & FAWS                                   |         |

| 5<br>6<br>7<br>8 | 6.2.2.1 Password Control (Optional)                                    |         |

| 7                | 6.2.2.2 Laser Frequency Setting Definition                             | 114     |

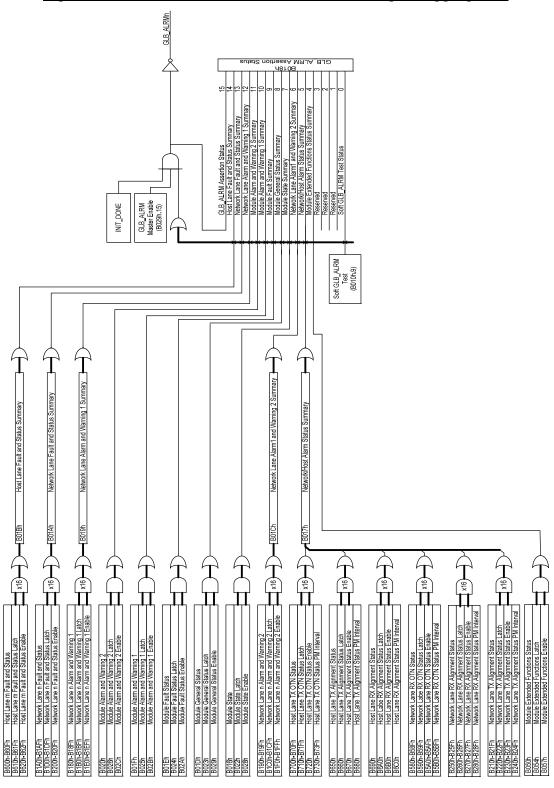

| 8                | 6.2.2.3 MSA-100GLH Module Global Alarm System Logic                    |         |

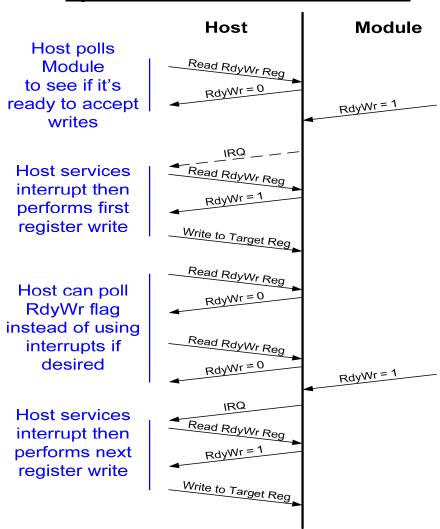

| 9                | 6.2.3 MDIO Write Flow Control                                          | 119     |

| 10               | 6.2.4 Module Monitored Parameters                                      | 120     |

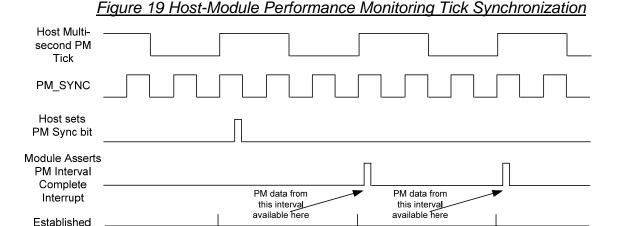

| 11               | 6.2.5 Performance Monitoring                                           | 120     |

| 12               | 6.2.5.1 Performance Monitoring Tick                                    | 120     |

| 13               | 6.2.5.2 Statistics                                                     |         |

| 14               | 6.2.5.3 Multi-Word Read Procedure                                      |         |

| 15               | 6.2.6 Software Upgrade Capability                                      |         |

| 16               | 6.2.7 Auxiliary Channel over MDIO (Optional)                           | 126     |

| 17               | 6.2.8 Module-to-Host Generic Data Upload                               | 128     |

| 18               | 6.2.9 Bulk Data Block Register Structure                               | 129     |

| 19               | 6.2.9.1 Host-to-Module Transaction Structure                           |         |

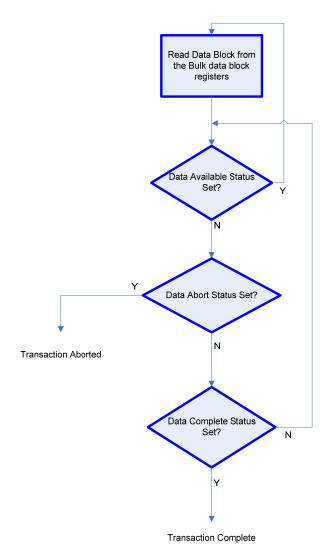

| 20               | 6.2.9.1 Module-to-Host Transaction Structure                           |         |

| 21               | 6.3 MSA-100GLH MODULE REGISTER OVERVIEW                                |         |

| 22               | 6.4 MSA-100GLH Module Register Description                             |         |

| 23               | 6.4.1 MSA-100GLH Module Network Lane Specific Register Tables          | 150     |

| 24               | 6.4.2 MSA-100GLH Module Host Lane Specific Register Tables             | 162     |

| 25               | 6.4.3 MSA-100GLH Network Lane VR2 Registers (Optional)                 |         |

| 26               | 6.5 CFP2-ACO REGISTERS                                                 |         |

| 27               | 6.5.1 Bulk Data Transfer Segment Registers                             |         |

|                  | o o                                                                    |         |

| 28               | 7 ADDENDUM A OIF CFP2 ACO MODULE IMPLEMENTATION AGREEME                | NT 169  |

# **REVISION HISTORY**

| Revision                                            | Date       | Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | By          |

|-----------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| External NDA Draft 0.1                              | 12/23/2008 | Initial release, work in progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Jiashu Chen |

| External NDA Draft 0.2                              | 01/26/2009 | 2 <sup>nd</sup> release for review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Jiashu Chen |

| External NDA Draft 0.3                              | 02/19/2009 | 3 <sup>rd</sup> release for review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Jiashu Chen |

| External NDA Draft 0.4E                             | 04/03/2009 | 4 <sup>th</sup> release for review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Jiashu Chen |

| External NDA Draft 0.4F                             | 04/07/2009 | Error corrected version of 0.4E for review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Jiashu Chen |

| Publication Draft 1.0                               | 04/13/2009 | First full draft for releasing to public.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Jiashu Chen |

| External NDA Draft 1.1                              | 6/22/2009  | Pre Public release Draft 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Jiashu Chen |

| External NDA Draft 1.2 R1                           | 8/31/2009  | Pre Public release Draft 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Jiashu Chen |

| External NDA Draft 1.2 R2                           | 9/14/2009  | Pre Public release Draft 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Jiashu Chen |

| External NDA Draft 1.2 R2C                          | 9/23/2009  | Pre Public release Draft 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Jiashu Chen |

| External NDA Draft 1.2 R2D                          | 9/29/2009  | Pre Public release Draft 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Jiashu Chen |

| Publication Draft 1.2                               | 9/30/2009  | Second full draft for release to public                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Jiashu Chen |

| External NDA Draft 1.3R5                            | 4/16/2010  | Pre Public Release for Draft 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Jiashu Chen |

| External NDA Draft 1.3R6                            | 5/20/2010  | Pre Public Release for Draft 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Jiashu Chen |

| Publication Version 1.4 (r1)                        | 6/4/2010   | Pre-Publication release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Jiashu Chen |

| Publication Version 1.4 (r2)                        | 6/4/2010   | Pre Publication release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Jiashu Chen |

| Publication Version 1.4 (r3)                        | 6/15/2010  | Pre Publication release for MSA Members                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Jiashu Chen |

| Publication Version 1.4 (r4)                        | 6/21/2010  | Pre Publication release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Jiashu Chen |

| Publication Version 1.4 (r5)                        | 6/22/2010  | Publication release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Jiashu Chen |

| Draft Version 2.0 (r7)                              | 6/30/2011  | Pre Publication release for public review. This release implements OIF MSA-100G DWDM Transmission Module Management Interface Requirements. Specifically, added new Section 6: MSA-100GLH Module Management Interface, which includes:  - Module Base and Extended ID Information;  - Module Command, Control & FAWS;  - MDIO Write Flow Control  - Additional Monitored Parameters and Performance Monitoring Functions for Long Haul DWDM;  - Software Upgrade Capability;  - Auxiliary Channel Interface over MDIO;  - Generic Data Upload Capability  - Bulk Data Transfer Procedure.  Added new Section 1.3: CFP MIS Version Compatibility.  This release also includes CFP MIS V1.4 updates:  - Sec. 4.10.2/Table 11: Note 2 is amended "Further commands should NOT be issued without returning to idle";  - Sec. 5.1/Table 18: 0x8007h, code point 09h = P111-3D1 (NRZ 40G 1300nm, 10km)  - Sec. 5.1/Table 18: 0x8071h.b2 & b1 changed to indicate whether Amplitude Adjustment Function is supported in A280h-A28Fh.  - Sec. 5.5/Table 22: A011h: Initial value changed to 1b=1/64 Tx Ref Clk Rate Select;  - Sec. 5.5/Table 22: A029h: Initial value changed to A7F8h Sec. 5.6/Table 23: A250h Initial value changed to E0DCh. See complete list of changes in file: | J. Anderson |

| B / f   f   1/2   2   2   2   2   2   2   2   2   2 | 0/00/50 10 | Comment_Log_CFP-MSA-MIS_V2p0_02_0312.xlsx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| Publication Version 2.0(r8)                         | 3/30/2012  | Pre Publication release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | J. Anderson |

| Publication Version 2.0(r9)                         | 4/10/2012  | Publication release See complete list of changes in file: Comment_Log_CFP-MSA-MIS_V2p0_01_0412.xlsx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | J. Anderson |

| Version 2.2r01                                      | 9/18/2012  | CFP MSA MIS 2.2 is released to support CFP2 and CFP2 applications, as well as enhancing all the contents from Version 2.0.  Version 2.2(r1) is released for review, representing work in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Jiashu Chen |

|                 |            | progress. Not final.                                           |                        |

|-----------------|------------|----------------------------------------------------------------|------------------------|

| Version 2.2r02  | 02/15/2013 | Pre-publication release                                        | Jiashu Chen            |

| Version 2.2r03  | 03/18/2013 | Pre-publication release. See complete list of changes in file: | Jiashu Chen            |

|                 |            | Comment_Log_CFP_MSA_MIS_V2p2r02_2013_03_18.xlsx                |                        |

| Version 2.2r04  | 04/29/2013 | Pre-Publication release. See complete list of changes in file: | Jiashu Chen            |

|                 |            | Commen_Log_CFP_MSA_MIS_V2p2r03_2013_04_21_update.xl            |                        |

|                 |            | SX                                                             |                        |

| Version 2.2r05c | 05/25/2013 | Publication release. See complete list of changes in file:     | Jiashu Chen            |

|                 |            | Comment_Log_CFP_MSA_MIS_V2p2r04_2013_05_25.xlsx                |                        |

| Version 2.2r06a | 07/01/2013 | Publication update. See complete list of changes in file:      | Jiashu Chen            |

|                 |            | Comment_Log_CFP_MSA_MIS_V2p2r05c_2013_07_01.xlsx               |                        |

| Version 2.4r01a | 01/31/2015 | Pre-publication release. See compete list of changes in file:  | Jiashu Chen            |

|                 |            | Comment_Log_CFP_MSA_V2p4_2015_01_31                            |                        |

| Version 2.4r03a | 03/27/2015 | Pre-publication release. See complete list of changes in file  | Jiashu Chen            |

|                 |            | Comment_Log_CFP_MSA_V2p4_2015_03_31                            |                        |

| Version 2.4r04a | 04/22/2015 | Pre-publication release. See complete list of changes in file  | Jiashu Chen            |

|                 |            | Comment_Log_CFP_MSA_V2p4_2015_04_22                            |                        |

| Version 2.4r05a | 06/01/2015 | Pre-publication release. See                                   | Jiashu Chen            |

|                 |            | Comment_Log_MIS_V2p4_Updated_2015_06_01.xls for change         |                        |

|                 |            | details                                                        |                        |

| Version 2.4r06b | 06/08/2015 | Publication release. See                                       | Jiashu Chen            |

|                 |            | Comment_Log_MIS_V2p4_Updated_2015_06_05.xls for change         |                        |

|                 | 22/22/22/2 | details.                                                       |                        |

| Version 2.6r02b | 09/06/2016 | Draft release for review. See                                  | Jiashu Chen            |

|                 |            | Comment_Log_MIS_V2p6_updated_2016_09_05.xls for change         |                        |

| 1/              | 00/05/0040 | details.                                                       | l'a a la concentration |

| Version 2.6r03a | 09/25/2016 | Draft release for review. See Comment-Log                      | Jiashu Chen            |

| Version 2.6r04a | 10/07/2016 | Draft release for review. See                                  | Jiashu Chen            |

| 1/              | 02/01/2017 | Comment_Log_MIS_V2p6_updated _2016_10                          | Jiashu Chen            |

| Version 2.6r05b | 02/01/2017 | Draft release for review. See                                  | Jiasnu Chen            |

| 1/ : 0.0.00     | 00/04/0047 | Comment_Log_MIS_V2p6_Updated_2017_01_27                        | " ' 0'                 |

| Version 2.6r06a | 03/24/2017 | Publication release. See                                       | Jiashu Chen            |

|                 |            | Comment_Log_MIS_V2p6_2017_03_24_Editor for change              |                        |

|                 |            | details                                                        |                        |

#### 1 **REFERENCES**

- 2 1. IEEE Standard 802.3-2012

- 3 2. IEEE Std. 802.3ba<sup>™</sup>-2010 (Obsolete, replaced by IEEE Standard 802.3-2012)

- 4 3. <u>INF-8074i, XENPAK MSA Issue 3.0</u>

- 4. INF-8077i, XFP Specification Rev. 4.5 (Not directly referenced)

- 6 5. CFP MSA Hardware Specification Draft 1.4

- 7 6. OIF-MSA-100GLH-EM-01.1, September, 2011

- 8 7. CFP MSA CFP2 HW Spec Rev02

- 9 8. CFP MSA CFP4 HW Spec

- 10 9. CFP MSA CFP8 HW Spec (draft)

LIST OF FIGURES

| 2  | Figure 1 CFP8 Module Port Address Reprogramming                          | 19  |

|----|--------------------------------------------------------------------------|-----|

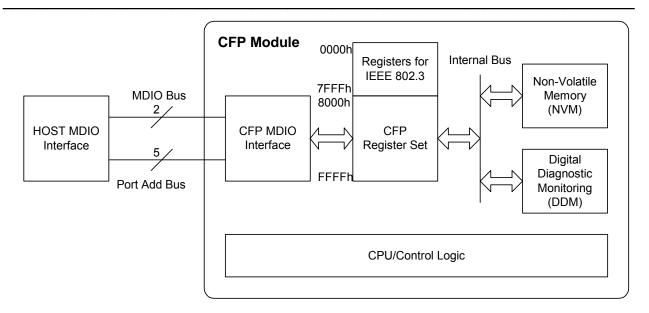

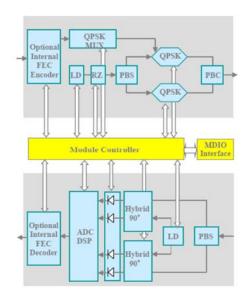

| 3  | Figure 2 CFP Management Interface Architecture                           | 20  |

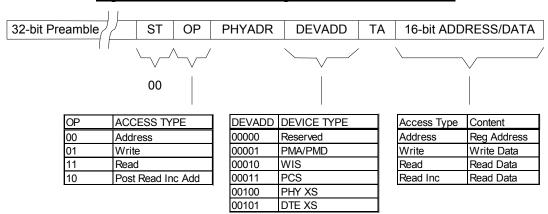

| 4  | Figure 3 CFP MDIO Management Frame Structure                             | 21  |

| 5  | Figure 4 State Transition Diagram during Startup and Turn-off            | 34  |

| 6  | Figure 5 Module Startup Sequence Example 1: No Host Transition Control   | 37  |

| 7  | Figure 6 Module Startup Sequence Example 2: Full Host Transition Control | 38  |

| 8  | Figure 7 Module Startup Sequence Example 3: Some Host Transition Control | 39  |

| 9  | Figure 8 Module Turn-off Sequence Example: No Host Transition Control    | 40  |

| 10 | Figure 9 Module Start-up Sequence Example: Operating in RX Only Mode     | 41  |

| 11 | Figure 10 FAWS Signal Model for a Single Bit                             | 43  |

| 12 | Figure 11 Global Alarm Signal Aggregation                                | 45  |

| 13 | Figure 12 CFP Built-in PRBS Components and Test Signal Flow              | 49  |

| 14 | Figure 13 Restore and Save Command Execution State Diagram               | 55  |

| 15 | Figure 14 Common Data Block Structure                                    |     |

| 16 | Figure 15 CDB Command Execution Flowchart                                | 64  |

| 17 | Figure 16 MSA-100GLH Module Management Architecture                      | 112 |

| 18 | Figure 17 MSA-100GLH Module Global Alarm Signal Aggregation              | 118 |

| 19 | Figure 18 Host-Module MDIO Write Flow Control                            | 119 |

| 20 | Figure 19 Host-Module Performance Monitoring Tick Synchronization        | 121 |

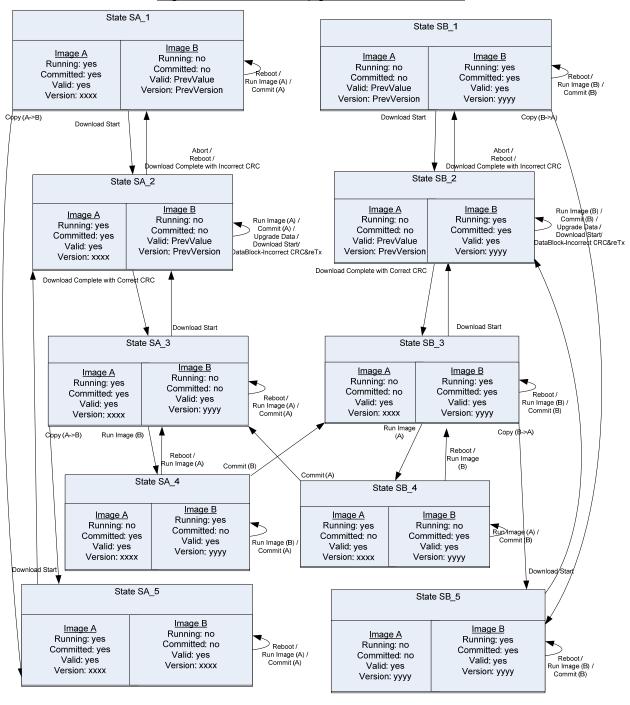

| 21 | Figure 20 Software Upgrade State Machine                                 | 124 |

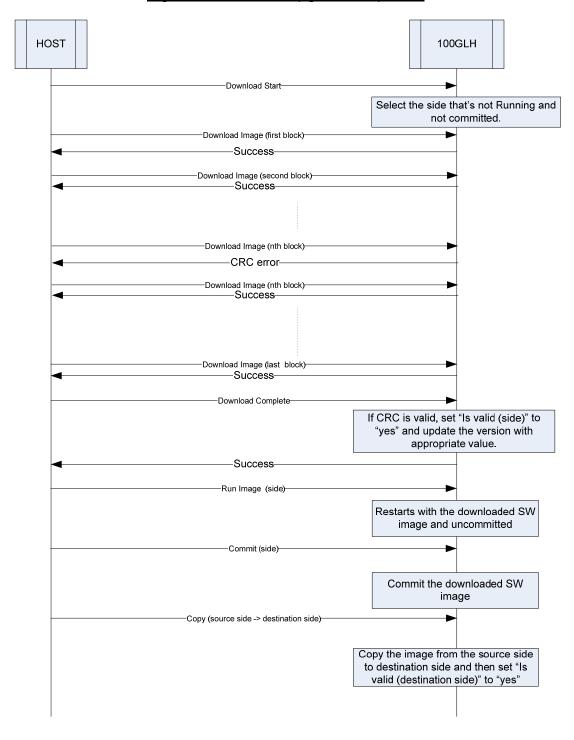

| 22 | Figure 21 Software Upgrade Sequence                                      | 125 |

| 23 | Figure 22 Host-to-Module Auxiliary Interface Data Transfer               | 126 |

| 24 | Figure 23 Module-to-Host Auxiliary Interface Data Transfer               | 127 |

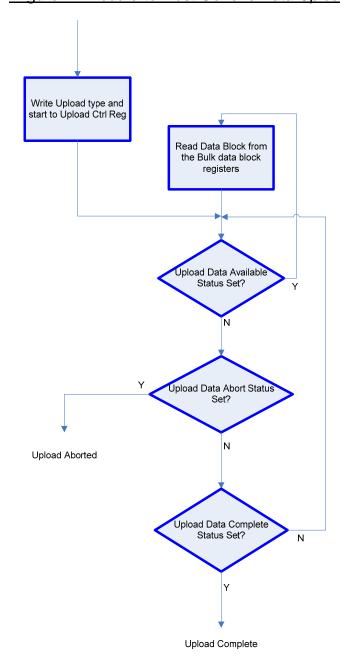

| 25 | Figure 24 Module-to-Host Generic Data Upload                             | 129 |

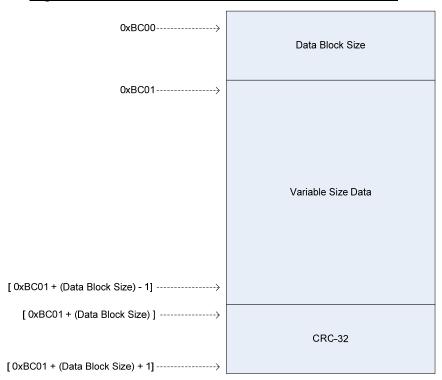

| 26 | Figure 25 Host-to-Module Bulk Data Block Structure                       | 130 |

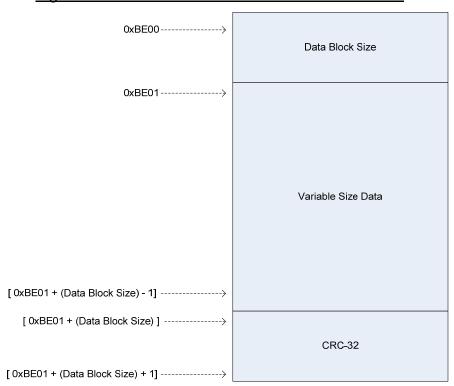

| 27 | Figure 26 Module-to-Host Bulk Data Block Structure                       | 131 |

| 28 |                                                                          |     |

# LIST OF TABLES

| 2  | Table 1 Glossary                                                  |     |

|----|-------------------------------------------------------------------|-----|

| 3  | Table 2 CFP Register Allocation                                   | 23  |

| 4  | Table 3 Bit Pattern of a Two's Complement Byte Data               | 25  |

| 5  | Table 4 Behavior of Signals Affected by Module State Transition   | 35  |

| 6  | Table 5 Behavior of FAWS Type in Different Module States          |     |

| 7  | Table 6 Global Alarm Related Registers                            |     |

| 8  | Table 7 Global Alarm Query Hierarchy                              | 44  |

| 9  | Table 8 Timing for Management Interface Control and Status        | 46  |

| 10 | Table 9 Miscellaneous Timing                                      |     |

| 11 | Table 10 CFP Ad-hoc Floating Point Number Examples                | 49  |

| 12 | Table 11: Register Access Password Requirements                   |     |

| 13 | Table 12 User NVRs Access Control Register (A004h)                | 52  |

| 14 | Table 13 Restore and Save Command State Definitions               |     |

| 15 | Table 14 Restore and Save Command State Transitions               |     |

| 16 | Table 15 HW Pin PRG_CNTL1, PRG_CNTL1 Pin State, and SOFT PRG_CNTL | 56  |

| 17 | Table 16 Programmable Control Functions                           |     |

| 18 | Table 17 Programmable Alarm Sources                               |     |

| 19 | Table 18 CDB Implementation                                       |     |

| 20 | Table 19 Write Flow Control to CDB Registers                      |     |

| 21 | Table 20 Acronyms used in CDB Command Table                       |     |

| 22 | Table 21 CDB Command Table                                        | 65  |

| 23 | Table 22 Table Column Description                                 | 68  |

| 24 | Table 23 CFP NVR 1                                                |     |

| 25 | Table 24 CFP NVR 2                                                |     |

| 26 | Table 25 CFP NVR 3                                                |     |

| 27 | Table 26 CFP NVR 4 Miscellaneous Registers                        |     |

| 28 | Table 27 CFP Module VR 1                                          |     |

| 29 | Table 28 MLG VR 1                                                 |     |

| 30 | Table 29 Network Lane VR 1                                        |     |

| 31 | Table 30 Network Lane VR 2                                        |     |

| 32 | Table 31 Network Lane VR 3 (Optional)                             |     |

| 33 | Table 32 Host Lane VR 1                                           |     |

| 34 | Table 33 Register Access Password Requirements                    |     |

| 35 | Table 34 MSA-100GLH Global Alarm Related Registers                |     |

| 36 | Table 35 Global Alarm Query Hierarchy                             | 117 |

| 37 | Table 36 MSA-100GLH Module Management Register Overview           | 131 |

| 38 | Table 37 MSA-100GLH Module VR 1 Registers                         |     |

| 39 | Table 38 Network Lane VR 3 (Optional)                             |     |

| 40 | Table 39 MSA-100GLH Module Network Lane VR 1 Registers            |     |

| 41 | Table 40 MSA-100GLH Module Network Lane VR 2 Registers            |     |

| 42 | Table 41 MSA-100GLH Module Host Lane VR 1 Registers               |     |

| 43 | Table 42 MSA-100GLH Network Lane VR 2 Registers                   | 166 |

| Table 43 CFP2-ACO New Registers            | 168 |

|--------------------------------------------|-----|

| Table 44 Bulk Data Transfer VR 2 Registers |     |

| <u> </u>                                   |     |

#### 1 DOCUMENT SUMMARY

#### 1.1 Background

This technical document, CFP MSA Management Interface Specification, has been created by the CFP MSA group as a basis for a technical agreement between CFP module users and vendors, together with its companion document CFP MSA Hardware Specification.

5 6 7

8

1

2

3

4

This document is not a warranted document. Each CFP or MSA-100GLH module supplier will have their own datasheet. If the users wish to find a warranted document, they should consult the datasheet of the chosen module vendor.

9 10 11

12

13

The CFP MSA group reserves the rights at any time to add, amend, or withdraw technical data contained in this document.

#### 1.2 CFP Management Interface

- 14 <u>CFP MSA Hardware Specification</u> specifies the use of Management Data Input/Output

- 15 (MDIO) as the management interface between a Host and a CFP module. While the

- hardware specification defines the hardware aspects of the MDIO interface such as its

- 17 electrical characteristics and timing requirements, this document defines a set of MDIO

- 18 registers suitable for CFP or MSA-100GLH module applications following MDIO interface

- 19 definition in IEEE 802.3 Clause 45.

# 20 1.3 CFP Management Interface Specification Version Compatibility

Version 1.4 (r5) is the first public publication release of the CFP Management Interface Specification supporting the CFP MSA Hardware Specification V1.4.

222324

25

26

27 28

21

Version 2.0 (r9) of the CFP Management Interface Specification is extended to support the OIF MSA-100GLH module electro-mechanical specification [6]. In particular, Section 6 is added in Version 2.0 which specifies added functionality and registers for supporting the OIF MSA-100GLH module management interface. Implementation of B000h page registers specified in Section 6 requires the use of Write Flow Control which is inherently incompatible with register write access implemented in Version 1.4.

29 30 31

32

33

34

To provide version backwards compatibility, A000h page registers specified in Version 1.4 are maintained in Version 2.0 without requiring Write Flow Control. The Version 2.0 A000h page registers are not extended or modified for supporting the OIF MSA-100GLH module management interface. There are some modifications to the Version 2.0 A000h page registers to correct errors in Version 1.4 A000h page registers.

35 36 37

38

39

40

To provide version forward compatibility, Version 1.4 A000h page registers are duplicated in the B000h page registers of Version 2.0 with enhancements and modifications for supporting the OIF MSA-100GLH module management interface. The B000h page registers requires Write Flow Control. In this manner, host system and module suppliers

may implement Version 2.0 B000h page registers for supporting both CFP MSA and OIF MSA-100GLH hardware specifications. A host system implementing Version 1.4 CFP MSA Management Interface Specification would not be compatible with modules implementing Version 2.0 CFP MSA Management Interface Specification.

4 5 6

7

8

1

3

Version 2.2 (r04) is the 3<sup>rd</sup> public publication release with the enhancement to support CFP2 and CFP4 modules, in particular the CFP MSA CFP2 Hardware Specification (Currently in Draft Revision 0.2). Majority of the changes are implemented in Sections from 1 to 5. Whenever it is applicable Section 6 is modified for consistency.

9 10 11

12

13

14

30

For the convenience of reference, new register names introduced in the subsequent releases are marked with version number such as [2.2] to indicate that this register is introduced in version 2.2 release. Similar approach has been applied to registers that were introduced in version 2.0.

#### 15 1.4 Content of this document

- 16 Section 1 is the summary of this document. Section 2 provides an overview of the CFP

- management interface, including a sample block diagram, MDIO command frame, and the

- 18 CFP register set. Section 3 layouts the overview of the CFP register set. Section 4

- 19 presents detailed discussions of the Host/Module control and signaling theory. Section 5

- 20 gives a series of tables describing the details of all CFP registers. Section 6 specifies

- 21 management interface functions and registers for supporting the OIF MSA-100GLH DWDM

- 22 Transmission Module.

## 23 **1.5 Notations**

# 24 1.5.1 Hardware Signal Name

- 25 Signals transmitted over CFP or MSA-100GLH module connector pins are considered as

- 26 hardware signals. Hardware signals names are directly quoted from the CFP MSA

- 27 Hardware Specification or MSA-100GLH, formed with all upper case letters and numbers

- 28 with the exception of a lower case letter as the post script for some cases. Examples are

- 29 MOD\_LOPWR and MOD\_RSTn.

# 1.5.2 Soft (MDIO) Signal Name

- 31 Signals transmitted over CFP Management Interface are considered as "Soft" signals or

- 32 MDIO signals. They are represented by CFP Registers or register bits. Soft signals have

- 33 their names denoted by one or more words or acronyms connected with or without

- 34 underscores. If the name consists of multiple words each word shall have its first character

- 35 capitalized. Examples are Soft GLB\_ALRM Test, Soft Module Reset, etc. Some Soft

- 36 signals used as the defaults for programmable hardware pins are denoted in the manner of

- 37 Hardware Signal names, such as GLB\_ALRM, HIPWR\_ON, and MOD\_READY.

#### 1.5.3 CFP Register Name and Address

- 2 The names of CFP registers are formed with one or more English words, with each word's

- 3 first character capitalized and space in between. Each register address is a 16-bit hex

- 4 number. When a particular bit in a register is addressed its address is denoted by x.y.

- 5 where the x is the register address and y is the bit address, a decimal number ranging from

- 6 0 to 15. When several bits in a register are addressed the address format is x.y~z, where y

- 7 and z are boundary bits. The sign "~" is used to represent all the bits in between.

#### 8 **1.5.4 Numbers**

1

- 9 Hex numbers are post-fixed by a lower case letter "h", for example, A000h. Binary

- 10 numbers are post-fixed by a lower case letter "b" such as 11b and 1101b. Decimal

- 11 numbers have neither prefix nor postfix. With this notation, an example of bit 15 at register

- 12 A001 (hex) has the format of A001h.15.

#### 13 1.5.5 Special Characters

- 14 Whenever possible, the special characters are avoided. For example, the symbol of

- 15 micrometer is designated as "um" or micro-meter instead of "μm" to prevent format loss in

- 16 the editing process.

#### 17 **1.6 Glossary**

- 18 The often used nomenclatures in this document are listed in the following glossary table for

- 19 reference.

20

## <u>Table 1 Glossary</u>

| Terminology            | Description                                                                                                                                                                                                  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APD                    | Avalanche Photodiode                                                                                                                                                                                         |

| BOL                    | Beginning Of Life                                                                                                                                                                                            |

| IEEE 802.3             | IEEE Standard 802.3-2012                                                                                                                                                                                     |

| CFP MSA Specifications | CFP MSA Specifications define a hot-pluggable optical transceiver form factor to enable 40Gbps and 100Gbps applications, including next-generation High Speed Ethernet (40GbE and 100GbE).                   |

|                        | CFP MSA Specifications consist of two major documents: CFP MSA Hardware Specification and CFP MSA Management Interface Specification (this document).                                                        |

| CFP module             | A transceiver compliant to CFP MSA. The term "module" refers to CFP module unless otherwise specified.                                                                                                       |

| CFP register(s)        | A CFP register collects certain related management information in a basic form of a 16-bit word, occupying one MDIO register address. The term "register" refers to CFP register unless otherwise specified. |

| CMU                    | Clock Multiplier Circuit.                                                                                                                                                                                    |

| Control                | It refers to the Host control functions to the module over Management Interface. It also includes the support of programmable control pin logic.                                                             |

| DDM                    | Digital Diagnostic Monitoring. It includes CFP module functions of A/D value reporting, FAWS logic, and programmable alarm pin logic.                                                                        |

| Terminology  | Description                                                                                                                                                                                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAWS         | Fault, Alarm, Warning, and Status.                                                                                                                                                                                 |

| GLB_ALRM     | It is a CFP module internally generated signal that drives GLB_ALRMn pin.                                                                                                                                          |

| GLB_ALRMn    | Global alarm hardware signal pin defined in CFP MSA Hardware Specification.                                                                                                                                        |

| HIPWR_ON     | High power mode of module operation.                                                                                                                                                                               |